## LV-PECL COMPATIBLE HIGH FREQUENCY VCXO IN LCC PACKAGE - VC75P1 Series

## FEATURES

- RoHS Compliant (Pb-Free), Wide Frequency Range

- Low Phase Jitter (4 ps at 155.52MHz) with New Generation PLL Design

- Leadless Chip Carrier Ultra Small Package with Industry de facto Standard Footprint

- Wide Frequency Pulling Range, APR = ±100 ppm

## **SPECIFICATIONS**

| Frequency Range                                                                                                                                                                                                                                                | 1 MHz to 800 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Voltage (Vcc)<br>Input Current<br>Control Voltage (Vc)<br>Storage Temperature<br>Frequency Stability / APR (Min)<br>Temperature Range<br>Standard Stability / Pullability<br>Duty Cycle                                                                  | B = +3.3 VDC $\pm$ 5%<br>100 mA Maximum<br>+1.65V $\pm$ 1.5V<br>-55°C to 125°C<br>C = $\pm$ 50 / $\pm$ 100 ppm<br>A = 0°C to 70°C; B = -40°C to 85°C<br>CA = $\pm$ 50 ppm / 0°C to 70°C, Absolute pull range (APR): $\pm$ 100 ppm Minimum<br>1 = Tristate 60/40% symmetry; 3 = Tristate 55/45% symmetry                                                                                                                                                                                                                     |

| Output Load<br>Logic "1" / Logic "0" Level<br>Rise/Fall Time (Tr/Tf)<br>Start-up time<br>Integrated Phase Jitter (RMS)<br>Modulation Bandwidth<br>Linearity / Slope<br>Input Impedance<br>Setability at Fnom, 25°C<br>Tristate Function<br>Enable/Disable Time | 50 Ohms to Vcc - 2.0V or Thevenin equivalent, Bias required<br>Vcc - 1.025V Minimum / Vcc - 1.620V Maximum<br>1 ns Maximum at 20% to 80% Vp-p<br>5 ms Maximum<br>4 ps Maximum for fj = 12KHz to 20MHz, at 155.520MHz<br>12 kHz Minimum at -3 dB<br>±20% Maximum of best straight line fit / Positive<br>50 kOhms Minimum, fm < 10KHz<br>+1.65V ±0.4V for 3.3V part<br>Input (Pin#2) High (2.2V Min) or open: Output (Pin#4, #5) active<br>Input (Pin#2) Low (0.4V Max): Output disabled in high impedance<br>100 ns Maximum |

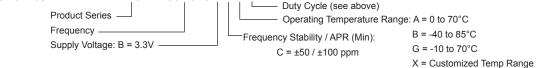

| Creating a Part Number<br>Product Seri                                                                                                                                                                                                                         | VC75P1-155M520-B C A 1<br>es Duty Cycle (see above)<br>Operating Temperature Dance: A = 0 to 70°C                                                                                                                                                                                                                                                                                                                                                                                                                           |

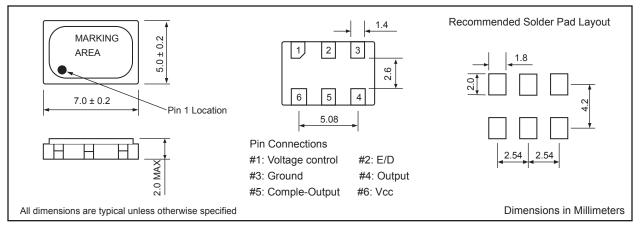

## **OUTLINE DRAWING**